# Japan Beyond 5G Promotion Consortium 7<sup>th</sup> Feb, 2024

# Open vRAN Infrastructure for Cloud and Edge Deployments

Raghu M. Rao AMD Fellow Adaptive and Embedded Computing Group

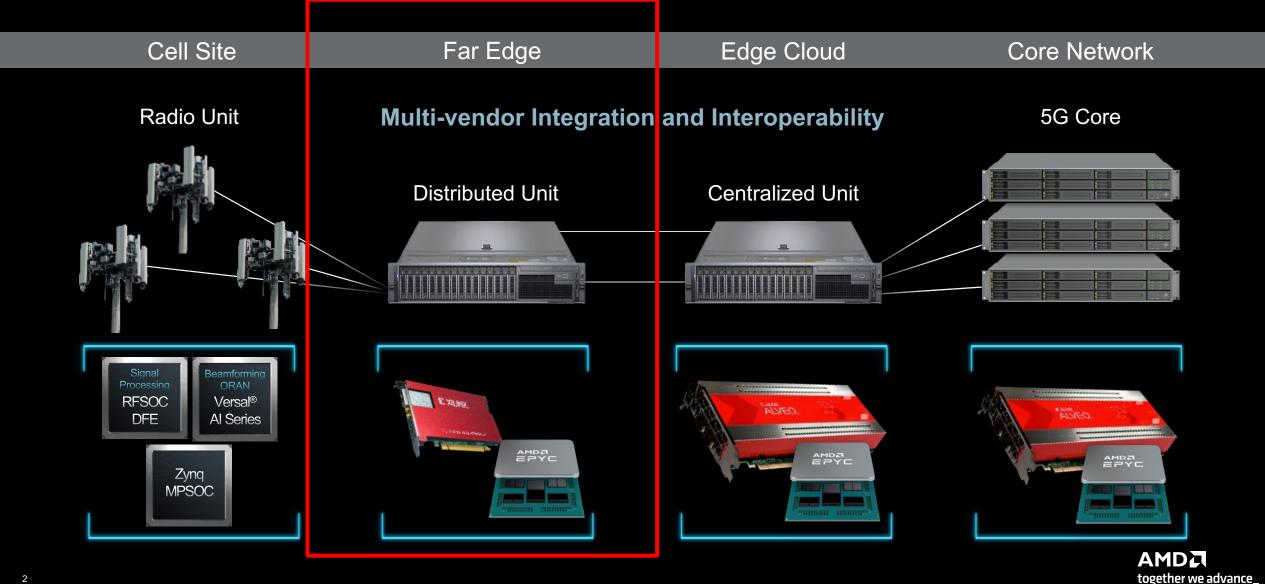

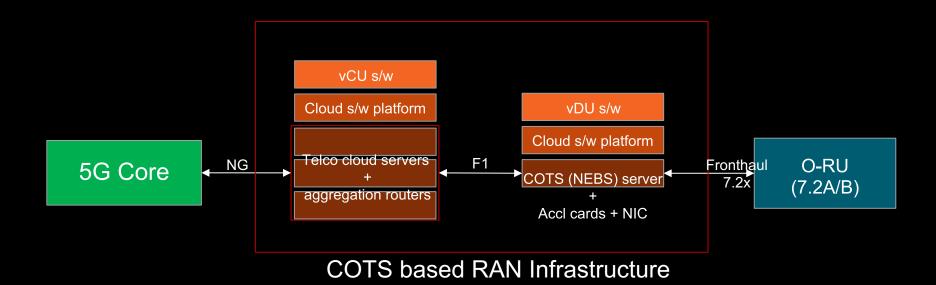

# The Disaggregated RAN Network

## **Open RAN Infrastructure**

- Separation of hardware and software

- Interfaces compliant with O-RAN standards

[Public]

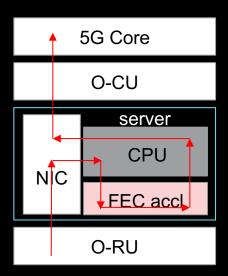

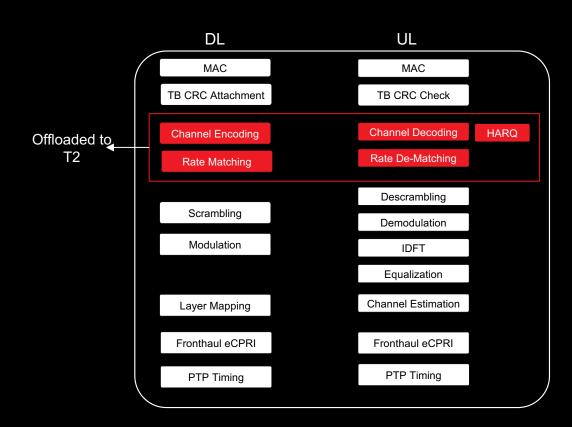

#### Inline v/s Look-aside

Look-aside FEC acceleration

- Layer 1 DL and UL processing on x86 cores

- LDPC enc/dec offloaded to accelerator

- Three key requirements

- PCIE bandwidth for FEC offload

- Compute capacity on the accelerator

- Number of x86 cores for L1, L2, etc.

Core scaling helps cost and energy efficiency

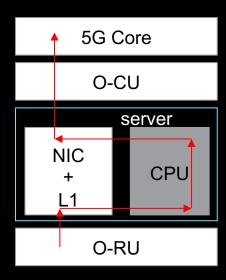

Inline acceleration

- Layer 1 offloaded to accel card, usually integrated w/ NIC

- Key requirements

- Fronthaul capacity (port count and data rates)

- Compute capacity of accelerator

- Number of X86 cores for L2

# The Telco Hardware Platform

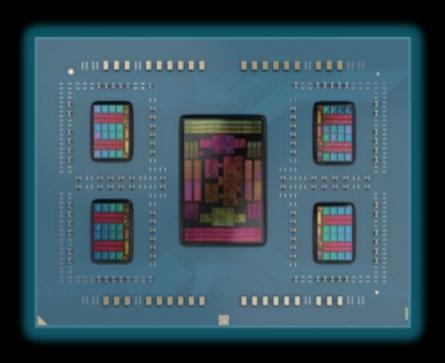

EPYC Zen 4c – 64 cores + T2 Accl

#### Optimal configuration-

- Number of cores

- Look-aside acceleration capacity

- PCIE bandwidth

Look-aside FEC acceleration

# **EPYC 8534 At A Glance**

| EPYC Zen4c - 8534PN                            |                                  |

|------------------------------------------------|----------------------------------|

| Core process technology                        | 5nm                              |

| Siena socket core count range                  | 8 – 64 (16 – 128 threads)        |

| Max # of Core Complex Dies (CCDs)              | 4                                |

| Max L3 cache size (per CCD)                    | 128 MB (32 MB)                   |

| Max # of memory channels                       | 6 channel DDR5 @ 4800 MT/s       |

| Max memory per socket                          | ЗТВ                              |

| Max lanes Peripheral<br>Component Interconnect | 96 lanes PCIe <sup>®</sup> Gen 5 |

| Max Processor Frequency                        | 3.15 GHz                         |

| Default TDP (64 cores)                         | 175W                             |

# T2 At A Glance

- High bandwidth look-aside (selected function) 5G NR LDPC accelerator

- O-RAN standards complaint DPDK / BBDev API

- Supports virtualization and orchestration

| PCle                   | 2x Gen 4x8        |

|------------------------|-------------------|

| Offload bandwidth      | 200 Gbps          |

| Profile                | HHHL              |

| LDPC FEC<br>Throughput | 33G Enc / 14G Dec |

| Power                  | <55W              |

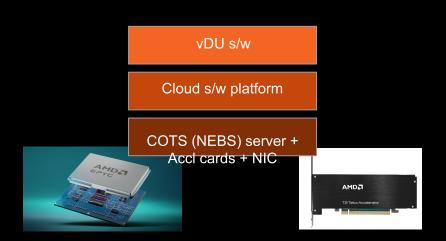

# The Telco Platform

EPYC Zen 4c – 64 cores + T2 Accl

#### Optimal configuration-

- Number of cores

- Look-aside acceleration capacity

- PCIE bandwidth

- Servers based on EPYC Zen4c processors are available from multiple vendors

- Cloud s/w support include Red Hat Openshift, and Ubuntu / Kubernetes.

- VMWare, WindRiver on the roadmap

- Multiple vRAN s/w vendors support AMD Telco platforms and others are evaluating the platform

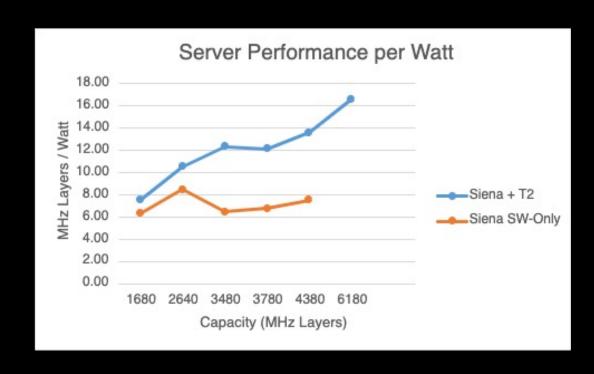

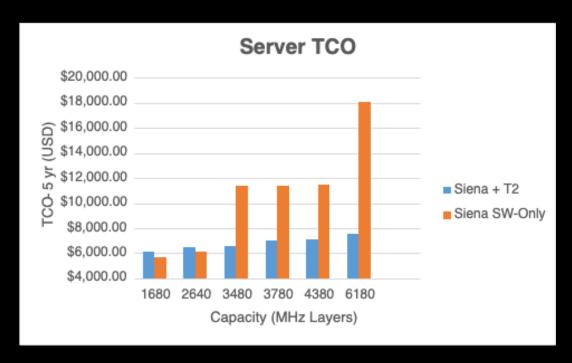

### **Power Efficiency And TCO Benefits of Acceleration**

Core scaling helps cost and energy efficiency

## Disclaimer and Attribution

The information contained herein is for informational purposes only and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale. GD-18

Use of third party marks / logos/ products is for informational purposes only and no endorsement of or by AMD is intended or implied. GD-83

© Copyright 2021 Advanced Micro Devices, Inc. All rights reserved. Xilinx, the Xilinx logo, AMD, the AMD Arrow logo, Alveo, Artix, EPYC, Kintex, Kria, Spartan, Versal, Vitis, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.